降低Tessent MemoryBIST解决方案Debug时间

Modern technologies like AI, IoT and other smart systems need a large amount of data storage leading to an increase in the usage of on-chip memory. As the size and number of memories in SoC designs increase, so do their testing requirements. Memories must be tested for their functionality thoroughly.

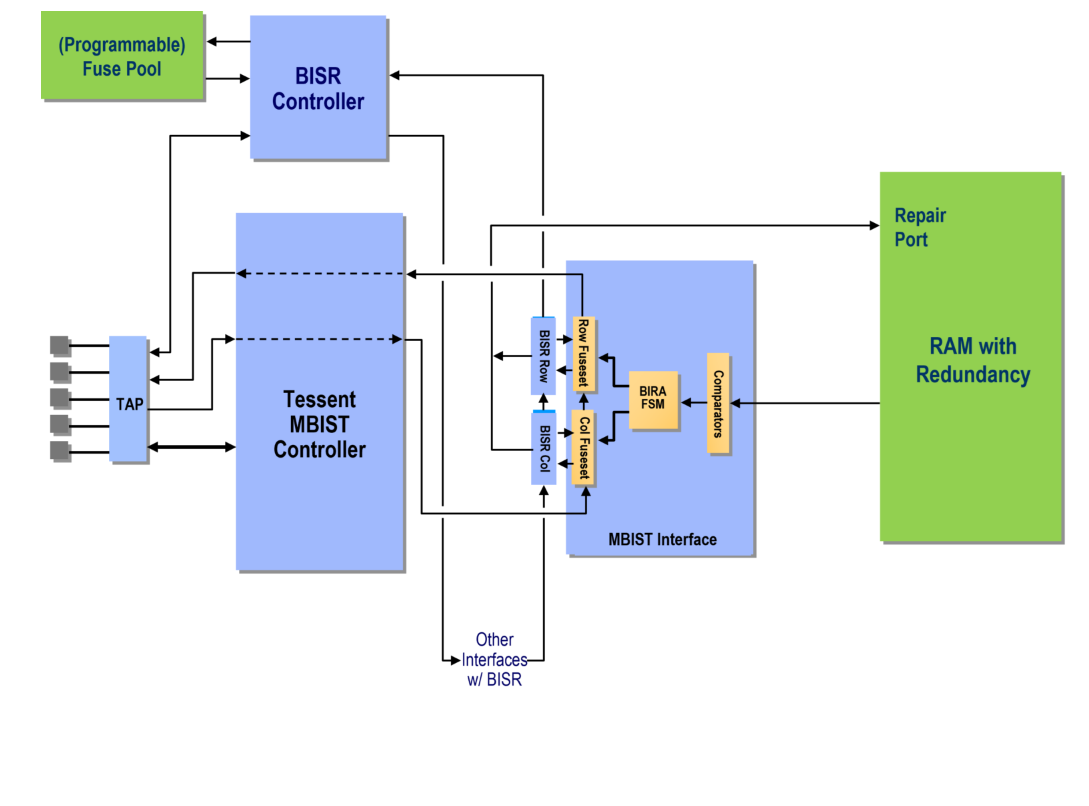

The Tessent™ MemoryBIST software and IP provides a complete solution for at-speed testing, diagnosis, repair, debug, and characterization of embedded memories. But often while testing the memories, customers encounter simulation mismatches . What are these simulation mismatches and how can we debug them easily?

MBIST simulation mismatch refers to a situation where there is a discrepancy or difference between the expected results of a memory built-in self-test (MBIST) simulation and the actual results obtained during the simulation. This can occur due to various reasons, such as errors in the MBIST operating protocol, issues with the debugging signals, or the possible root causes for any unexpected mis-compares in the simulation.

This series of videos from Tessent guides users to debug MBIST simulation mismatches Tessent MBIST Simulation Mismatch (siemens.com).

Here is also a list of suggested articles/videos that helps with various aspects of the Memory BIST flow Tessent Memory BIST – Suggested articles and videos (siemens.com).

有关更多Tessent MBIST解决方案的支持和培训信息, 请浏览Support Center:https://support.sw.siemens.com and Siemens’ Xcelerator Academy Siemens Xcelerator Academy

更多技术文章请浏览Siemens Tessent微博:EDA Support Blogs - Siemens Software